# 08: MCU datasheets ct'd

### Project

Brainstorm/propose projects on Ed thread Project matching form will release early next week Project must: Use PWM, ADC, or DAC Have at least one interrupt service routine Have a watchdog timer (doesn't count as your ISR)

Use at least one of: Serial communication, Wifi, Timer/counter

# Why we're thinking about the project so early

Time to find you resources

Time to refine the design

Time to order supplies

Time for embedded SE process

# Skills in upcoming labs

don't call yourself a "gamer"

if you haven't played this game!

#### Incredible work on your projects, CS 1600! We want to brag about you! - Arun, Jason, Stephen, and Prof. Zizyte

# **Keywords for sharing data**

### static

Value of local variable will persist between function calls (is in **memory** rather than the stack)

Useful in a function like loop() when you don't want to declare a global variable Still local to the function

### volatile

Means variable can change outside of main execution (e.g. by an ISR) **Always use volatile when working with variables that change in ISRs!** Tells compiler not to make certain optimizations (never keep value in a register)

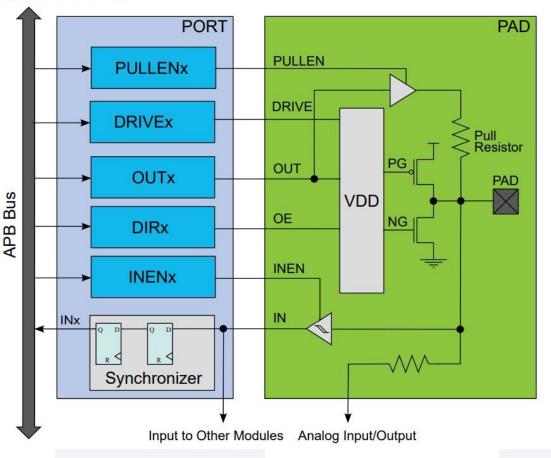

#### 23.6 Functional Description

Figure 23-2. Overview of the PORT

**Goal of "bare** metal programming" is to configure bits inside of the peripheral registers (blue), which directly control the hardware (green)

### **Dependencies for using DAC**

#### 35.5.1 I/O Lines

Using the DAC Controller's I/O lines requires the I/O pins to be configured using the port configuration (PORT).

#### **Related Links**

23. PORT - I/O Pin Controller

#### 35.5.3 Clocks

The DAC bus clock (CLK\_DAC\_APB) can be enabled and disabled by the Power Manager, and the default state of CLK\_DAC\_APB can be found in the *Peripheral Clock Masking* section.

A generic clock (GCLK\_DAC) is required to clock the DAC Controller. This clock must be configured and enabled in the Generic Clock Controller before using the DAC Controller. Refer to GCLK – Generic Clock Controller for details.

This generic clock is asynchronous to the bus clock (CLK\_DAC\_APB). Due to this asynchronicity, writes to certain registers will require synchronization between the clock domains. Refer to 35.6.7 Synchronization for further details.

#### **Related Links**

16.6.2.6 Peripheral Clock Masking

15. GCLK - Generic Clock Controller

# **Configuring pin in PORT for DAC**

23.6.3.1 Pin Configurations Summary

Table 23-2. Pin Configurations Summary

| DIR | INEN | PULLEN | Ουτ | Configuration                             |

|-----|------|--------|-----|-------------------------------------------|

| 0   | 0    | 0      | Х   | Reset or analog I/O: all digital disabled |

# Multiplexing

- I/O on MCU comes in many varieties: GPIO, DAC, ADC, PWM, interrupts, timers/counters, communication

- Limited # of pins on device pins can be configured to have one of multiple purposes

- Multiplexing is the word for selecting this purpose

#### Pin(1) B(2)(3) I/O Pin Supply D G SERCOM(2)(3) SAMD2xG ADC TC(4) SAMD2xE SAMD2xJ EIC REF AC PTC DAC SERCOM-ALT TCC сом AC/ GCLK 1 1 1 PA00 VDDANA EXTINT[0] SERCOM1/ TCC2/WO[0] PAD[0] 2 2 2 PA01 VDDANA EXTINT[1] SERCOM1/ TCC2/WO[1] PAD[1] 3 PA02 VDDANA 3 3 EXTINT[2] AIN[0] Y[0] VOUT TCC3/ WO[0]

#### Table 7-1. PORT Function Multiplexing for SAM D21 A/B/C/D Variant Devices and SAM DA1 A/B Variant Devices

### **PMUX register in PORT**

#### 23.8.12 Peripheral Multiplexing n

| Name:     | PMUX                  |

|-----------|-----------------------|

| Offset:   | 0x30 + n*0x01 [n=015] |

| Reset:    | 0x00                  |

| Property: | PAC Write-Protection  |

### name of register

There are up to 16 Peripheral Multiplexing registers in each group, one for every set of two subsequent I/O lines. The n denotes the number of the set of I/O lines.

| Bit    | 7          | 6  | 5  | 4  | 3  | 2    | 1      | 0  |

|--------|------------|----|----|----|----|------|--------|----|

|        | PMUXO[3:0] |    |    |    |    | PMUX | E[3:0] |    |

| Access | RW         | RW | RW | RW | RW | RW   | RW     | RW |

| Reset  | 0          | 0  | 0  | 0  | 0  | 0    | 0      | 0  |

### roles/names of bits inside the register

### Values for named bits

Bits 3:0 - PMUXE[3:0] Peripheral Multiplexing for Even-Numbered Pin

These bits select the peripheral function for even-numbered pins (2\*n) of a PORT group, if the corresponding PINCFGy.PMUXEN bit is '1'.

Not all possible values for this selection may be valid. For more details, refer to the *I/O Multiplexing and Considerations*.

| PMUXE[3:0] | Name | Description                    |

|------------|------|--------------------------------|

| 0x0        | А    | Peripheral function A selected |

| 0x1        | В    | Peripheral function B selected |

| 0x2        | С    | Peripheral function C selected |

| 0x3        | D    | Peripheral function D selected |

| 0x4        | E    | Peripheral function E selected |

| 0x5        | F    | Peripheral function F selected |

| 0x6        | G    | Peripheral function G selected |

| 0x7        | Н    | Peripheral function H selected |

| 0x8        | I    | Peripheral function I selected |

### **Configuring DAC**

- 35.6 Functional Description

- 35.6.1 Principle of Operation

The DAC converts the digital value located in the Data register (DATA) into an analog voltage on the DAC output (VOUT).

A conversion is started when new data is written to the Data register. The resulting voltage is available on the DAC output after the conversion time. A conversion can also be started by input events from the Event System.

#### 35.6.2 Basic Operation

#### 35.6.2.1 Initialization

The following registers are enable-protected, meaning they can only be written when the DAC is disabled (CTRLA.ENABLE is zero):

- Control B register (CTRLB)

- Event Control register (EVCTRL)

Enable-protection is denoted by the Enable-Protected property in the register description.

Before enabling the DAC, it must be configured by selecting the voltage reference using the Reference Selection bits in the Control B register (CTRLB.REFSEL).

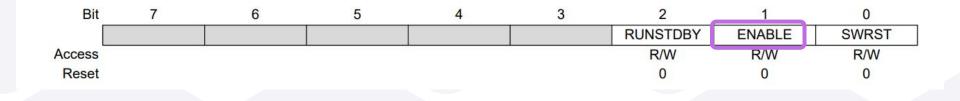

#### 35.6.2.2 Enabling, Disabling and Resetting

The DAC Controller is enabled by writing a '1' to the Enable bit in the Control A register (CTRLA.ENABLE). The DAC Controller is disabled by writing a '0' to CTRLA.ENABLE.

The DAC Controller is reset by writing a '1' to the Software Reset bit in the Control A register (CTRLA.SWRST). All registers in the DAC will be reset to their initial state, and the DAC Controller will be disabled. Refer to the CTRLA register for details.

#### 35.6.2.3 Enabling the Output Buffer

To enable the DAC output on the V<sub>OUT</sub> pin, the output driver must be enabled by writing a one to the External Output Enable bit in the Control B register (CTRLB.EOEN).

The DAC output buffer provides a high-drive-strength output, and is capable of driving both resistive and capacitive loads. To minimize power consumption, the output buffer should be enabled only when external output is needed.

#### 35.6.2.4 Digital to Analog Conversion

The DAC converts a digital value (stored in the DATA register) into an analog voltage. The conversion range is between GND and the selected DAC voltage reference. The default voltage reference is the internal reference voltage. Other voltage reference options are the analog supply voltage (VDDANA) and the external voltage reference (VREFA). The voltage reference is selected by writing to the Reference Selection bits in the Control B register (CTRLB.REFSEL).

The output voltage from the DAC can be calculated using the following formula:

$$V_{\rm OUT} = \frac{\rm DATA}{0x3\rm FF} \cdot \rm VREF$$

A new conversion starts as soon as a new value is loaded into DATA. DATA can either be loaded via the APB bus during a CPU write operation, using DMA, or from the DATABUF register when a START event occurs. Refer to 35.6.5 Events for details. As there is no automatic indication that a conversion is done, the sampling period must be greater than or equal to the specified conversion time.

# What this means

Setup:

- Select reference (CTRLB.REFSEL)

- Enable (CTRLA.ENABLE)

Operation:

• Write 10-bit value to DATA

$$V_{\rm OUT} = \frac{\rm DATA}{\rm 0x3FF} \cdot \rm VREF$$

#### 35.8.2 Control B

| Name:     | CTRLB                                  |

|-----------|----------------------------------------|

| Offset:   | 0x01                                   |

| Reset:    | 0x00                                   |

| Property: | PAC Write-Protection, Enable-Protected |

Note: I misspoke about this in class. We need to use VDDANA, which is the supply voltage (3.3 V) that powers the chip, NOT INTREF.

| Bit    | 7    | 6       | 5 | 4    | 3   | 2       | 1    | 0    |

|--------|------|---------|---|------|-----|---------|------|------|

|        | REFS | EL[1:0] |   | BDWP | VPD | LEFTADJ | IOEN | EOEN |

| Access | R/W  | R/W     |   | R/W  | R/W | R/W     | R/W  | R/W  |

| Reset  | 0    | 0       |   | 0    | 0   | 0       | 0    | 0    |

#### Bits 7:6 – REFSEL[1:0] Reference Selection

This bit field selects the Reference Voltage for the DAC.

| Value | Name   | Description                | Description                |  |  |  |

|-------|--------|----------------------------|----------------------------|--|--|--|

| 0x0   | INTREF | Internal voltage reference | Internal voltage reference |  |  |  |

| 0x1   | VDDANA | Analog voltage supply      |                            |  |  |  |

| 0x2   | VREFA  | External reference         | External reference         |  |  |  |

| 0x3   |        | Reserved                   | Reserved                   |  |  |  |

#### 35.8.1 Control A

| Name:     | CTRLA                                    |

|-----------|------------------------------------------|

| Offset:   | 0x00                                     |

| Reset:    | 0x00                                     |

| Property: | PAC Write-Protection, Write-Synchronized |

#### Bit 1 - ENABLE Enable DAC Controller

Due to synchronization there is delay from writing CTRLA.ENABLE until the peripheral is enabled/disabled. The value written to CTRLA.ENABLE will read back immediately and the corresponding bit in the Synchronization Busy register (SYNCBUSY.ENABLE) will be set. SYNCBUSY.ENABLE will be cleared when the operation is complete.

| Value | Description                                   |

|-------|-----------------------------------------------|

| 0     | The peripheral is disabled or being disabled. |

| 1     | The peripheral is enabled or being enabled.   |

#### 35.8.8 Data DAC

| Name:     | DATA                                     |

|-----------|------------------------------------------|

| Offset:   | 0x08                                     |

| Reset:    | 0x0000                                   |

| Property: | PAC Write-Protection, Write-Synchronized |

| Bit    | 15 | 14 | 13 | 12   | 11     | 10 | 9 | 8 |

|--------|----|----|----|------|--------|----|---|---|

|        |    |    |    | DATA | [15:8] |    |   |   |

| Access | W  | W  | W  | W    | W      | W  | W | W |

| Reset  | 0  | 0  | 0  | 0    | 0      | 0  | 0 | 0 |

|        |    |    |    |      |        |    |   |   |

| Bit    | 7  | 6  | 5  | 4    | 3      | 2  | 1 | 0 |

|        |    |    |    | DATA | A[7:0] |    |   |   |

| Access | W  | W  | W  | W    | W      | W  | W | W |

| Reset  | 0  | 0  | 0  | 0    | 0      | 0  | 0 | 0 |

#### Bits 15:0 - DATA[15:0] Data value to be converted

DATA register contains the 10-bit value that is converted to a voltage by the DAC. The adjustment of these 10 bits within the 16-bit register is controlled by CTRLB.LEFTADJ.

#### Table 35-1. Valid Data Bits

| CTRLB.LEFTADJ | DATA       | Description             |

|---------------|------------|-------------------------|

| 0             | DATA[9:0]  | Right adjusted, 10-bits |

| 1             | DATA[15:6] | Left adjusted, 10-bits  |

### Final to-do list:

- Configure dependencies

- PORT: select Multiplexer function B for PA02

- GCLK: configure GCLK\_DAC

- Configure DAC peripheral

- Select reference (CTRLB.REFSEL)

- Enable (CTRLA.ENABLE)

- Operate DAC peripheral

### Using the header files

The header file for each peripheral has definitions that begin with [PERIPHERAL NAME]\_[REGISTER NAME]. So, if we want to use PORT's PMUX register, we look for PORT\_PMUX in port.h

| 282                  | /* PORT_PMUX : (PORT Offset: 0x30) (R/W 8) GROUP Peripheral Multiplexing n */ |                                                 |                                                         |  |  |  |

|----------------------|-------------------------------------------------------------------------------|-------------------------------------------------|---------------------------------------------------------|--|--|--|

| 283                  | <pre>#if !(defined(ASSEMBLY)    defined(IAR_SYSTEMS_ASM))</pre>               |                                                 |                                                         |  |  |  |

| 284                  | typedef union {                                                               |                                                 |                                                         |  |  |  |

| 285                  | <pre>struct {</pre>                                                           |                                                 | definition of the hit                                   |  |  |  |

| 286                  | uint8_t PMUXE:4; /*!<                                                         | bit: 0 3 Peripheral Multiplexing Even           | */ definition of the bit                                |  |  |  |

| 287                  | uint8_t PMUXO:4; /*!<                                                         | bit: 4 7 Peripheral Multiplexing Odd            | */ locations/names within the                           |  |  |  |

| 288                  | } bit; /*!<                                                                   | Structure used for bit access                   | */ register                                             |  |  |  |

| 289                  | uint8_t reg; /*!<                                                             | Type used for register access                   | */ register                                             |  |  |  |

| 290                  | <pre>} PORT_PMUX_Type;</pre>                                                  |                                                 |                                                         |  |  |  |

| 291                  |                                                                               |                                                 |                                                         |  |  |  |

| 292                  |                                                                               |                                                 |                                                         |  |  |  |

| 293                  | <pre>#define PORT_PMUX_OFFSET</pre>                                           | 0x30 /**< \brief (PORT_PMUX offset) Per         | ipheral Multiplexing n */                               |  |  |  |

| this mask has 294    | <pre>#define PORT_PMUX_RESETVALUE</pre>                                       | 0x00 /**< \brief (PORT_PMUX reset_value         | ) Peripheral Multiplexing n */                          |  |  |  |

| 1s in all of the 295 |                                                                               |                                                 |                                                         |  |  |  |

| bits of PMUXE 296    | <pre>#define PORT_PMUX_PMUXE_Pos</pre>                                        | 0 /**< \brief (PORT_PMUX) Peripheral            | Multiplexing Even */                                    |  |  |  |

| and Os 297           | #define PORT PMUX PMUXE Msk                                                   | (0xFu << PORT PMUX PMUXE Pos)                   | definitions for values PMUXE                            |  |  |  |

| everywhere 298       | <pre>#define PORT_PMUX_PMUXE(value)</pre>                                     | ((PORT_PMUX_PMUXE_Msk & ((value) << PORT_PMUX_P | MUXE_Pos))) bits take on: offset of those               |  |  |  |

| 200                  | <pre>#define PORT_PMUX_PMUXE_A_Val</pre>                                      | 0x0u /**< \brief (PORT_PMUX) Peripheral         | function A selected ~/                                  |  |  |  |

| else. See how 300    | <pre>#define PORT_PMUX_PMUXE_B_Val</pre>                                      | 0x1u /**< \brief (PORT_PMUX) Peripheral         | function B selected */ bits within the register, values |  |  |  |

| we could use it 301  | <pre>#define PORT_PMUX_PMUXE_C_Val</pre>                                      | 0x2u /**< \brief (PORT_PMUX) Peripheral         | function c selected */ that these bits can take on      |  |  |  |

| on the next 302      | <pre>#define PORT_PMUX_PMUXE_D_Val</pre>                                      | 0x3u /**< \brief (PORT_PMUX) Peripheral         | function D selected */                                  |  |  |  |

| slide 303            | <pre>#define PORT_PMUX_PMUXE_E_Val</pre>                                      | 0x4u /**< \brief (PORT_PMUX) Peripheral         | function E selected */                                  |  |  |  |

| 304                  | <pre>#define PORT_PMUX_PMUXE_F_Val</pre>                                      | 0x5u /**< \brief (PORT_PMUX) Peripheral         | function F selected */                                  |  |  |  |

| 305                  | <pre>#define PORT_PMUX_PMUXE_G_Val</pre>                                      | 0x6u /**< \brief (PORT_PMUX) Peripheral         | function G selected */                                  |  |  |  |

| 306                  | #define PORT PMUX PMUXE H Val                                                 | 0x7u /**< \brief (PORT PMUX) Peripheral         | function H selected */                                  |  |  |  |

| 307                  | <pre>#define PORT_PMUX_PMUXE_A</pre>                                          | (PORT_PMUX_PMUXE_A_Val << PORT_PMUX_PMU         | XE_Pos)                                                 |  |  |  |

| 308                  | <pre>#define PORT_PMUX_PMUXE_B</pre>                                          | (PORT_PMUX_PMUXE_B_Val << PORT_PMUX_PMU         |                                                         |  |  |  |

| 309                  | <pre>#define PORT_PMUX_PMUXE_C</pre>                                          | (PORT_PMUX_PMUXE_C_Val << PORT_PMUX_PMU         | <pre>xE_Pos) these are the relevant</pre>               |  |  |  |

| 310                  | <pre>#define PORT_PMUX_PMUXE_D</pre>                                          | (PORT_PMUX_PMUXE_D_Val << PORT_PMUX_PMU         | xE_Pos) definitions (values shifted                     |  |  |  |

| 311                  | <pre>#define PORT_PMUX_PMUXE_E</pre>                                          | (PORT_PMUX_PMUXE_E_Val << PORT_PMUX_PMU         | XE_Pos) definitions (values shifted                     |  |  |  |

| 312                  | <pre>#define PORT_PMUX_PMUXE_F</pre>                                          | (PORT_PMUX_PMUXE_F_Val << PORT_PMUX_PMU         | <b>to the correct position</b>                          |  |  |  |

| 313                  | <pre>#define PORT_PMUX_PMUXE_G</pre>                                          | (PORT_PMUX_PMUXE_G_Val << PORT_PMUX_PMU         | XE_Pos)                                                 |  |  |  |

| 314                  | <pre>#define PORT_PMUX_PMUXE_H</pre>                                          | (PORT_PMUX_PMUXE_H_Val << PORT_PMUX_PMU         | XE_Pos)                                                 |  |  |  |

### Writing the correct value to PMUX

#### // Select MUX function B for PA02

#### PORT->Group[PORTA].PMUX[1].reg = PORT\_PMUX\_PMUXE\_B;

// Note that the above would overwrite the PMUXO bits.

// If we need to keep them (i.e. if we're also configuring PA01),

// we should use bit operations and masking, e.g.

- // PORT->Group[PORTA].PMUX[1].reg &= ~PORT\_PMUX\_PMUXE\_Msk

- // (To clear the PMUXE bits using a mask)

- // PORT->Group[PORTA].PMUX[1].reg |= PORT\_PMUX\_PMUXE\_B

- // (To set the value of those bits without affecting the other bits)

In dac.h:

Note that the name doesn't exactly match up with the datasheet (VDDANA), but the value the header file defines (0x1) does. This is probably for compatibility reasons with related boards – as long as we've double-checked that we match the datasheet, we can use this

| _ |     |    |                                               |             |                                                    |

|---|-----|----|-----------------------------------------------|-------------|----------------------------------------------------|

|   | 110 |    | <pre>#define DAC_CTRLB_REFSEL_Msk</pre>       | (0x3u << D/ | AC_CTRLB_REFSEL_Pos)                               |

|   | 111 |    | <pre>#define DAC_CTRLB_REFSEL(value)</pre>    | ((DAC_CTRLE | B_REFSEL_Msk & ((value) << DAC_CTRLB_REFSEL_Pos))) |

|   | 112 |    | <pre>#define DAC_CTRLB_REFSEL_INT1V_Val</pre> | 0x0u        | /**< \brief (DAC_CTRLB) Internal 1.0V reference */ |

| ſ | 113 |    | #define DAC_CTRLB_REFSEL_AVCC_Val             | 0x1u        | /**< \brief (DAC_CTRLB) AVCC */                    |

|   | 114 |    | #define DAC_CTRLB_REFSEL_VREFP_Val            | l 0x2u      | /**< \brief (DAC_CTRLB) External reference */      |

|   | 115 |    | <pre>#define DAC_CTRLB_REFSEL_INT1V</pre>     | (DAC_CTRLB  | _REFSEL_INT1V_Val << DAC_CTRLB_REFSEL_Pos)         |

|   | 116 |    | <pre>#define DAC_CTRLB_REFSEL_AVCC</pre>      | (DAC_CTRLB  | _REFSEL_AVCC_Val << DAC_CTRLB_REFSEL_Pos)          |

|   | 117 |    | <pre>#define DAC_CTRLB_REFSEL_VREFP</pre>     | (DAC_CTRLB  | _REFSEL_VREFP_Val << DAC_CTRLB_REFSEL_Pos)         |

|   |     | 72 | <pre>#define DAC_CTRLA_SWRST_Pos</pre>        | 0           | /**< \brief (DAC_CTRLA) Software Reset */          |

|   |     | 73 | <pre>#define DAC_CTRLA_SWRST</pre>            | (0x1u <<    | DAC_CTRLA_SWRST_Pos)                               |

|   |     | 74 | <pre>#define DAC_CTRLA_ENABLE_Pos</pre>       | 1           | /**< \brief (DAC_CTRLA) Enable */                  |

|   | ſ   | 75 | <pre>#define DAC_CTRLA_ENABLE</pre>           | (0x1u <<    | DAC_CTRLA_ENABLE_Pos)                              |

|   |     | 76 | <pre>#define DAC_CTRLA_RUNSTDBY_Pos</pre>     | 2           | /**< \brief (DAC_CTRLA) Run in Standby */          |

|   |     | 77 | <pre>#define DAC_CTRLA_RUNSTDBY</pre>         | (0x1u <<    | DAC_CTRLA_RUNSTDBY_Pos)                            |

|   |     | 78 | <pre>#define DAC_CTRLA_MASK</pre>             | 0x07u       | /**< \brief (DAC_CTRLA) MASK Register */           |

|   |     |    |                                               |             |                                                    |

### setup function

void setup() {

// \*\* Configure PORT \*\*

// Reset config bits for PA02 and enable MUX: TODO (see example in lab 3)

// Select MUX function B for PA02

PORT->Group[PORTA].PMUX[1].reg = PORT\_PMUX\_PMUXE\_B;

// \*\* Configure GCLK DAC \*\*

// TODO (see example in lab 3)

// \*\* Configure DAC \*\*

// Select internal voltage reference

DAC->CTRLB.reg = DAC\_CTRLB\_REFSEL\_AVCC;

// Enable DAC

#### DAC->CTRLA.reg = DAC\_CTRLA\_ENABLE;

// We could have also done this using bit manipulation, e.g.:

// DAC->CTRLA.reg = (1 << 1); // Move value 1 to bit position 1</pre>

### **loop function: DAC operation**

#### void loop() {

// Output 2.5V on DAC pin

// Compute DAC value for 2.5 V

// (write 25/33 instead of 2.5/3.3 to avoid floating point division)

#### unsigned int dac val = 1023 \* 25 / 33;

// Write to DAC DATA register

DAC->DATA.reg = dac\_val;